# Statistical Design Optimization of FinFET SRAM Using Back-Gate Voltage

Behzad Ebrahimi, Masoud Rostami, Ali Afzali-Kusha, and Massoud Pedram

Abstract— In this paper, an optimal approach for the design of 6-T FinFET based SRAM cells is proposed. The approach considers the statistical distributions of gate length and silicon thickness and their corresponding statistical correlations due to process variations. In this method, a back-gate voltage is used as the optimization knob. With the help of Particle Swarm Optimization (PSO), the back-gate voltages that maximize the yield of the SRAM array against read, write, and access time failures are found. It will be shown that with this method a very high yield may be achieved.

*Index Terms*—SRAM, FinFET, yield, process variations, design for manufacturability, back-gate design.

## I. INTRODUCTION

Since SRAM arrays are a major part of the chip area in the state of the art microprocessors [1], their scaling has been a driving for the technology shrinkage. As the device dimensions diminish, the magnitude and effects of parametric variations have been exacerbated. Statistical variability along with scaling of the supply and threshold voltages has degraded the stability of six-transistor (6-T) SRAM cells [2]. In recent years, several statistical schemes have been proposed to maximize the immunity against these variations [3], [4]. For example, the substrate voltage was used in [4] to increase the stability of SRAMs against process variations.

The FinFET [5] transistor structure is one of the attractive options to replace the conventional planar technology due to its improved scalability and gate controllability. In these devices, the gates on either side of the fin can be tied together or electrically isolated to allow an independent biasing scheme. In the tied-gates operating mode the two gates are biased together to switch the FinFET on/off [6]. In the independent-gates operating mode, it is possible to design the device in a way that one gate is used to switch the FinFET on/off and the other one is used to adjust the threshold voltage. This offers dynamic or static performance tunability which gives designers a great flexibility [7]. In [8], authors used this feature to improve the SRAM cell stability. They used two different wordlines that were connected to the front and back gates of each access transistors. In another work, an independent-gate FinFET SRAM has also been successfully manufactured with a considerable leakage reduction [9].

In this work<sup>1</sup>, we propose to use the back-gate voltage of FinFET to maximize the yield of the SRAM cell based on these devices against parametric failures. The rest of the paper is organized as follows. Different failure mechanisms in SRAM cells are reviewed in Section II. In Section III, expressions for the read and write stability, read current, and

subthreshold power of SRAM cell are presented. The proposed method for the yield optimization will be introduced in Section IV while the results of this method are discussed in Section V. Finally, Section VI concludes the paper.

## II. FAILURE MECHANISMS IN SRAM CELLS

In this section, these failure mechanisms are briefly reviewed.

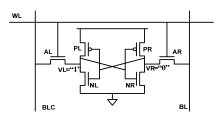

**Read Failure:** It occurs due to the corruption of the stored data in the cell while accessing it. During the read operation of the cell shown in Fig. 1 (VL="1" and VR="0"), the voltage at node R (VR) increases to a positive value, denoted by  $V_{\rm read}$ , due to the voltage division between the right access transistor (AR) and the right pull down transistor (NR). If  $V_{\rm read}$  is higher than the trip point of the left inverter (PL - NL), denoted by  $V_{\rm trip}$ , then the cell flips and a read failure occurs.

Write Failure: It is the inability to change the stored data. If the stored data is "1" and we intend to write "0" into it, the node L becomes discharged through BLC to a lower value. This value is determined by the voltage division between the left PMOS pull up transistor (PL) and the left access transistor (AL). If VL cannot be reduced below the trip point of the right inverter (PR - NR) then a write failure occurs.

Access Time Failure: It is the inability to produce a predefined voltage difference (e.g.,  $\Delta \min \approx 0.1 V_{\rm dd}$ ) between the bitlines in the allocated time slot ( $T_{\rm max}$ ) during the read operation.

# III. MODELING OF SRAM FAILURE METRICS

In this section, we present accurate yet simple models for efficiently estimating the failure metrics of the SRAM FinFET. These models are used in the yield optimization in the presence of the process variations. Since our optimization may affect the subthreshold power, we also present the model used for estimating the subthreshold power in this section.

In this work, asymmetrical FinFET  $(n^+/p^+)$  polysilicon gate for n-channel and  $p^+/n^+$  one for p-channel transistors) are considered. The nominal values of key device parameters are summarized in Table I. For implementing the proposed scheme, we also assume that all transistors have one fin to achieve a compact layout area.

Fig. 1. Schematic of a conventional 6-T SRAM cell.

Table I. Nominal device parameters used for device simulation.

| t <sub>ox</sub> (Oxide Thickness)  | 1 nm                               |

|------------------------------------|------------------------------------|

| $t_{\rm si}$ (Silicon Thickness)   | 10 nm                              |

| $V_{\rm dd}$ (Power Supply)        | 1 V                                |

| N <sub>body</sub> (Channel Doping) | $2 \times 10^{16} \text{ cm}^{-3}$ |

| H (Fin Height)                     | 60 nm                              |

|                                    |                                    |

<sup>&</sup>lt;sup>1</sup> Preliminary version of this work has been presented in *International Conference on Computer and Communication Engineering*, May 2008, Malaysia.

# A. Threshold Voltage

In the asymmetrical FinFET, the back-gate channel is rarely formed, and hence, for modeling its current, the front threshold voltage ( $V_{thf}$ ) is sufficient. This threshold voltage can be found using [11]

$$V_{\rm thf} = V_{\rm th \, (4T\text{-}DGMOS)} - rV_{\rm bg}. \tag{1}$$

where  $V_{\rm bg}$  is the back-gate voltage, r is the gate-to-gate coupling factor, and

$$V_{\text{th (4T-DGMOS)}} = (1+r) V_{\text{th (3T-DGMOS)}}. \tag{2}$$

The gate-to-gate coupling factor is given by

$$r = \frac{3t_{\text{fox}}}{3t_{\text{box}} + t_{\text{si}}}.$$

(3)

where  $t_{\text{fox}}$  and  $t_{\text{box}}$  are front and back oxide thicknesses, respectively, and  $t_{\text{si}}$  is the silicon body thickness. In (2),  $V_{\text{th(3T-DGMOS)}}$  can be calculated using [12]

$V_{\text{th(3T-DGMOS)}} = V_{\text{th-long-ch}} + \Delta V_{\text{th-DIBL}} + \Delta V_{\text{th-SCIBL}}$

$$= \frac{E_{g}}{2q} + \phi_{B} + \frac{(\phi_{Gfs} + \phi_{Gbs}) - (\frac{Q_{b}}{C_{fox}} - r\frac{Q_{b}}{2C_{Si}})}{1 + r} - \frac{3t_{Si}t_{fox}V_{ds}}{L_{g}^{2}} - \frac{9t_{Si}t_{fox}(\frac{E_{g}}{2q})}{L_{g}^{2}}.$$

(4)

where  $E_{\rm g}$  is the band gap of the silicon, q is the electric charge,  $\Phi_{\rm B}$  is the Fermi potential of the silicon body,  $\Phi_{\rm Gfs}$  and  $\Phi_{\rm Gbs}$  are the work function differences between the front-gate and body and the back-gate and body, respectively,  $Q_{\rm b}$  is the depletion charge density of the channel,  $C_{\rm fox}$  and  $C_{\rm Si}$  are the front gate capacitance per unit area ( $\varepsilon_{\rm si}/t_{\rm fox}$ ) and the body capacitance per unit area ( $\varepsilon_{\rm si}/t_{\rm si}$ ), respectively,  $L_{\rm g}$  is the channel length and  $V_{\rm ds}$  is the drain-source voltage. The short channel induced barrier lowering (SCIBL) and drain induced barrier lowering (DIBL) effects are also taken into account. In our device, the thickness of the body is large enough (10nm) for neglecting the quantum effects [12].

# B. On-Current

For a good estimation of the *on*-current, the  $n^{th}$  power law model [13] is used. The current expressions for the saturation  $(I_{Dsat})$  and linear modes  $(I_{Dlin})$  are given by, respectively,

$$I_{\text{Dsat}} = \frac{H}{L_{\text{g}}} B (V_{\text{gs}} - V_{\text{thf}})^n \quad V_{\text{ds}} \ge V_{\text{Dsat}}$$

(5)

$$I_{\text{Dlin}} = I_{\text{Dsat}} \left(2 - \frac{V_{\text{ds}}}{V_{\text{Dsat}}}\right) \frac{V_{\text{ds}}}{V_{\text{Dsat}}} \quad V_{\text{ds}} < V_{\text{Dsat}}$$

(6)

where H is the fin height and

$$V_{\text{Dsat}} = K(V_{\text{gs}} - V_{\text{thf}})^m. \tag{7}$$

In these equations, m, n, B and K are fitting parameters which are found by fitting the above equations to the results obtained from the device simulations [14]. In the device simulations, the drift-diffusion model along with high field saturation was used for transport. The carrier mobilities were also calibrated using the experimental data for FinFETs [15].

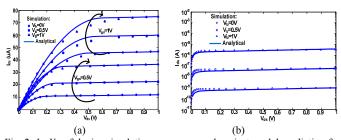

Fig. 2.  $I_{\rm ds}$ - $V_{\rm ds}$  of device simulations are compared against model prediction for an *n*-channel FinFET with device parameters in Table I and 45nm channel length for a) *on*-current b) Subthreshold current when  $V_{\rm gs}$ =0.

The FinFET *on*-currents as a function of  $V_{\rm ds}$  are given in Fig. 2(a) which reveals a good accuracy for the model.

## C. Subthreshold Current

The major components of the static leakage current for FinFET transistors include both the gate tunneling and subthreshold currents. The front-gate leakage is nearly independent of the back-gate in asymmetrical DG transistors. It was shown by device simulation that by variation of the back-gate voltage between 0 and  $V_{\rm dd}$ , the front-gate leakage had a variation of less than 5% but the subthreshold leakage varied between two and three orders of magnitude because of the strong dependence on the threshold voltage. Also, note that the use of high dielectric materials has lowered the gate tunneling current. In this work, we only consider the subthreshold current in the optimization of the standby power.

The subthreshold current in a double-gate FinFET can be expressed as [16]

$$I_{\text{Dsub}} = A \frac{H}{L_{\text{g}}} t_{\text{si}} \exp(\frac{V_{\text{gs}} - V_{\text{thf}}}{b}) (1 - \exp(\frac{-qV_{\text{ds}}}{KT})). \tag{8}$$

where K is the Boltzmann constant, T is the temperature in Kelvin and, A and b are the fitting parameters. Fig. 2(b) shows a close match of the predicted subthreshold current in FinFET with the simulation results.

# D. Read Stability

$V_{\rm trip} - V_{\rm read}$  can be considered as a good metric for the read stability of the cell [17]. For a stable read operation, it must be positive.  $V_{\rm trip}$  can be found from the KCL equation at node L when VL and VR are set to  $V_{\rm trip}$  as [17]

$$\begin{split} I_{\mathrm{Dsat-NL}}(V_{\mathrm{fg}} &= V_{\mathrm{trip}}, V_{\mathrm{S}} = 0, V_{\mathrm{d}} = V_{\mathrm{trip}}) \\ &= I_{\mathrm{Dsat-PL}}(V_{\mathrm{fg}} = V_{\mathrm{trip}}, V_{\mathrm{s}} = V_{\mathrm{dd}}, V_{\mathrm{d}} = V_{\mathrm{trip}}) \\ &+ I_{\mathrm{Dsat-AL}}(V_{\mathrm{fg}} = V_{\mathrm{dd}}, V_{\mathrm{s}} = V_{\mathrm{trip}}, V_{\mathrm{d}} = V_{\mathrm{dd}}). \end{split} \tag{9}$$

$V_{\text{read}}$  may also be found from the KCL equation at node R during the read operation assuming VL to be  $V_{\text{dd}}$  as [17]

$$I_{\text{Dsat-AR}}(V_{\text{fg}} = V_{\text{dd}}, V_{\text{s}} = V_{\text{read}}, V_{\text{d}} = V_{\text{dd}})$$

$$= I_{\text{Dlin-NR}}(V_{\text{fg}} = V_{\text{dd}}, V_{\text{s}} = 0, V_{\text{d}} = V_{\text{read}}). \tag{10}$$

The read stability will be the highest if the back-gate voltages are set to zero. The reason is explained as follows. There are two ways to increase the read stability. First, we can increase  $V_{\rm trip}$  which is achieved by increasing the threshold voltage of the pull up transistor and decreasing the threshold voltage of pull down transistor. Second, one should increase

the resistance of the access transistor and hence lower  $V_{\text{read}}$  which may be obtained by increasing the threshold voltage of the access transistors.

# E. Write Stability

The write stability metric or write margin (WM) can be defined (for the case of Fig. 1) as the maximum BLC voltage that is able to flip the cell state while BL is kept high [6]. WM must be positive to consider the cell "write stable". In the write state, PL and AL divide the bitline voltage between each other. Assuming that there is not enough time for VR to increase and switch NL to the OR state, OR can be calculated from the KCL at OR when OR is set to the OR to the OR as

$$I_{ds-AL}(V_{fg} = V_{dd}, V_s = WM, V_d = V_{trip})$$

=  $I_{ds-PL}(V_{fg} = 0, V_s = V_{dd}, V_d = V_{trip}).$  (11)

We should find the region of operation of AL and PL at these biases to solve this equation. First,  $V_{\rm trip}$  can be found as before from (9).  $V_{\rm Dsat\text{-}AL}$  and  $V_{\rm Dsat\text{-}PL}$  which are the drain saturation voltages can be found from (7). Comparing  $V_{\rm trip}$  to  $V_{\rm Dsat\text{-}AL}$  and  $V_{\rm Dsat\text{-}PL}$ , different regions of operation may be recognized. For example, if  $V_{\rm Dsat\text{-}AL} < V_{\rm trip} < V_{\rm Dsat\text{-}PL}$ , we use the saturation current models for both transistors.

To increase the write stability, the access transistor should be strengthened while the pull down and pull up transistors should be weakened. This makes the back to back inverters weak and hence breaking the feedback becomes easier. So the optimum back-gate voltages are 1V, 0V, and 1V for the access, pull down, and pull up transistors, respectively.

# G. Read Current

Read current is the indicator of the access time. As the read current increases, the access time decreases. In the read mode, the voltage of the node storing zero is raised to  $V_{\rm read}$ . The current of the access transistor in this situation is the read current that discharges the proper bitline. This voltage lowering enables the sense amplifier to detects the zero and complete the read operation. The read current is considered as the saturation current of the access transistor when  $V_{\rm fg} = V_{\rm dd}$ ,  $V_{\rm s} = V_{\rm read}$ , and  $V_{\rm d} = V_{\rm dd}$ .  $V_{\rm read}$  can be calculated using (10).

The value of the bitline capacitance is estimated from our previous work and simulation results as 22.5fF [10]. The minimum read current can be obtained easily from (12).  $\Delta min$  is set to be 0.1V in this paper.

$$I_{\min} = \frac{C_{\text{bitline}} \Delta min}{T_{\text{max}}}.$$

(12)

In our model, while the pull up transistor does not have any effect on the access current, the pull down transistor should be chosen as strong as possible for reducing  $V_{\rm read}$  and enhancing the overdrive voltage of the access transistor. Increasing the strength of the access transistors will yield two contradictory results; it increases its drive capability while at the same time it increases  $V_{\rm read}$  and decreases the overdrive voltage of access transistor. The simulation results revealed that the former effect is the dominant one, and hence, the choice of the backgate voltages as 1V for both the access, and pull down transistors will lead to the highest read current.

## H. Subthreshold Leakage Power

Consider the SRAM cell shown in Fig. 1. When  $VL = V_{\rm dd}$  and VR = 0, the right access, left pull down, and right pull up transistors have subthreshold leakage. If the values of the storage nodes are complemented, the other three transistors will consume subthreshold leakage power.

In SRAM arrays, we can assume symmetric cases where half of the cells have stored "1" and the other half have stored "0" [17]. The subthreshold leakage power can be modeled as

$$StaticPower = \frac{1}{2}(I_{\rm Dsub-AR}(V_{\rm fg} = 0, V_{\rm s} = 0, V_{\rm d} = V_{\rm dd}) \\ + I_{\rm Dsub-NR}(V_{\rm fg} = 0, V_{\rm s} = 0, V_{\rm d} = V_{\rm dd}) + I_{\rm Dsub-PR}(V_{\rm fg} = V_{\rm dd}, V_{\rm d} = 0) \\ + I_{\rm Dsub-AL}(V_{\rm fg} = 0, V_{\rm s} = 0, V_{\rm d} = V_{\rm dd}) \\ + I_{\rm Dsub-NL}(V_{\rm fg} = 0, V_{\rm s} = 0, V_{\rm d} = V_{\rm dd}) + I_{\rm Dsub-PL}(V_{\rm fg} = V_{\rm dd}, V_{\rm d} = 0)). \tag{13}$$

Since  $V_{\rm dd}$  is equal to 1V, the subthreshold current may be considered as the subthreshold power (static power). High power consumption may not lead to functional failures but it will shorten the battery lifetime. In this work, we assume that our subthreshold power budget is  $2\mu A$  per cell [18].

# IV. OPTIMIZATION METHODOLOGY

In this section, first, we discuss the random parameters in the SRAM cell. In addition, we describe a simple yield function used in our optimization. Finally, the implementation details of our optimization method are explained.

## A. SRAM Probabilistic Variables

The channel length  $(L_{\sigma})$  and the silicon thickness  $(T_{Si})$  of FinFETs are considered to be the major sources of the parametric variations in FinFETs [6]. The variations can be divided into local and global variations. The local variations are uncorrelated (r = 0) while the global variations of neighboring transistors are assumed to be completely correlated (r = 1) [19]. The local and global variances of  $L_g$ and  $T_{Si}$  are estimated to be  $3\sigma = 10\%$  of their nominal values. This estimation is derived from the data reported in [20]. These variations are approximated to be Gaussian [20]. It should be noted that since the channel in the devices is lightly doped, random dopant fluctuation can be ignored. To consider the imperfection in the circuit that produces the back-gate voltages, we considered a standard deviation of 0.05V for each of these voltages. Thus, we have 30 random variables in the optimization space. Among them, 12 variables represent local variations and 12 variables represent global variations of  $L_{\rm g}$ and  $T_{Si}$ . The remaining six variables represent different backgate voltages. Note that nominal values of  $L_g$  and  $T_{Si}$  are determined by the technology while the optimization process provides us with the optimum values of the back-gate voltages.

## B. Yield Modeling

In Section III, models for each SRAM metrics were proposed. We assume that each metric has a Gaussian distribution which is related to the 30 random variables via a function. Denoting the metric by y, we may write

$$y = f(x_1, ..., x_{30}). (14)$$

where  $x_1,...,x_{30}$  are the Gaussian random variables with averages of  $\eta_1,...,\eta_{30}$  and standard deviations of  $\sigma_1,...,\sigma_{30}$ .  $r_{(i,k)}$  is the correlation coefficient between  $x_i$  and  $x_j$ . The mean and variance of the random variable y can be estimated as [17]

$$\mu_{y} = f(\eta_{1},...,\eta_{30}) + \frac{1}{2} \sum_{i=1}^{30} \frac{\partial^{2} f}{\partial x_{i}^{2}} \Big|_{\eta_{i}} \sigma_{i}^{2}$$

$$+ \sum_{k=1}^{30} \sum_{i=1;i\neq k}^{30} \frac{\partial^{2} f}{\partial x_{i}} \Big|_{\eta_{i},\eta_{k}} r_{(i,k)} \sigma_{i} \sigma_{k}.$$

$$\sigma_{y}^{2} = \sum_{i=1}^{30} (\frac{\partial f}{\partial x_{i}} \Big|_{\eta_{i}})^{2} \sigma_{i}^{2}$$

$$+ 2 \sum_{k=1}^{30} \sum_{i=1;i\neq k}^{30} (\frac{\partial f}{\partial x_{i}} \Big|_{\eta_{i}}) (\frac{\partial f}{\partial x_{k}} \Big|_{\eta_{k}}) r_{(i,k)} \sigma_{i} \sigma_{k}.$$

$$(15)$$

We define each metric such that if it is positive, there will be no failure. The read and write stability metrics already have this condition (by assuming zero noise margin as in [17]), and hence, we only need to redefine the read current metric as

ReadCurrent (New) = ReadCurrent (Old) –  $I_{min}$  (17) where  $I_{min}$  is obtained from (12). Therefore, the failure probability for each metric is defined as

$$P[y_{\rm F}] = P[y < 0]. \tag{18}$$

The general failure probability is defined as

$$P[All] = P[R_F + W_F + A_F]$$

=  $P_{RF} + P_{WF} + P_{AF} - P[A_F R_F] - P[A_F W_F].$  (19)

where  $R_F$ ,  $W_F$ , and  $A_F$  are the read, write, and access time failures, respectively. To evaluate (19), we need to have the joint CDF of y and z which is given by

$$P[y \le 0, z \le 0] = \int_{y=-\infty}^{0} \int_{z=-\infty}^{0} N_{y,z}(y : \mu_{y}, \sigma_{y}; z : \mu_{z}, \sigma_{z}) dy dz$$

$$N_{y,z}(y, z) = \frac{1}{2\pi\sigma_{y}\sigma_{z}\sqrt{1 - \rho^{2}}}$$

$$\times \exp \left[ -\frac{(\frac{y - \mu_{y}}{\sigma_{y}})^{2} - 2\rho(\frac{y - \mu_{y}}{\sigma_{y}})(\frac{z - \mu_{z}}{\sigma_{z}}) + (\frac{z - \mu_{z}}{\sigma_{z}})^{2}}{2(1 - \rho^{2})} \right]. (20)$$

The correlation coefficient  $\rho$  can be computed from

$$\rho = \frac{E(yz) - E(y)E(z)}{\sigma(y)\sigma(z)} = \frac{E(yz) - \mu_y \mu_z}{\sigma(y)\sigma(z)}.$$

(21)

where yz is a function of 30 variables and E(yz) can be found from (15).

In our calculations, we assumed that  $P[R_FW_F]$  was negligible and the probability of simultaneous occurrence of three failures was zero. Finally, the yield may be found from

$$Yield = 1 - P[ALL]. (22)$$

## C. Yield Optimization

Based on the above discussion, our problem is converted to finding the maximum of the yield in the design. To find the optimum point in the parametric space, any nonlinear or evolutionary optimization technique can be employed. Evolutionary algorithms have the advantage of faster convergence and lower probability of being trapped in local optima. Particle Swarm Optimization (PSO) has been used in

this paper as the engine of optimization due to ease of implementation and having continuous variables [21]. The algorithm is initiated by placing handful of agents with random velocity and location in the space of parameters. Their locations and velocities are modified using the following equation [21] after each iteration:

$$V_{id} = W_{inertia}V_{id} + C_{1}rand()(P_{id} - X_{id}) + C_{2}rand()(P_{gd} - X_{id})$$

$$X_{id} = X_{id} + V_{id}.$$

(23)

where,  $C_1$  and  $C_2$  are constants, the rand() is a function which returns a value from a uniform distribution between 0 and 1,  $X_{\rm id}$  and  $V_{\rm id}$  are the location and velocity of each agent,  $W_{\rm inertia}$  is the inertia weight of the algorithm,  $P_{id}$  is the location of the best place that any agent has encountered in the whole time of the simulation, and  $P_{\rm gd}$  is the location of the best global point in the parameter space that all the agents have found in the current iteration. As can be seen from the above formula, each agent has a memory which saves the best location that it has found so far and pursues it in its subsequent moves. Also, all the agents are capable of broadcasting their best found location to their neighborhood. The value of the yield function of (22) is taken as the fitness function of the evolutionary algorithm. The agents were defined as points in a three dimensional space where each dimension represents the backgate voltage of one of access, pull down, or pull up devices. The search space is also confined by the maximum allowable leakage power which was chosen to be 2µW in this work.

## V. RESULTS AND DISCUSSION

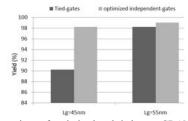

The optimization process was applied to 45nm and 55nm channel lengths where we assumed the same process parameters (as given in Table 1).  $T_{\rm max}$  was selected to be 75ps [17] for the channel length of 45nm and 100ps for the channel length of 55nm to compensate for the decreased strength due to the channel length increase. The optimum back-gate voltages obtained from the PSO algorithm are provided in Table II. Fig. 3 compares the yield for the optimized cell with that of tied-gates one. The results, which were obtained after 10,000 Monte Carlo simulations, show that the proposed technique increases the yield by 8.8% and 0.8% for the channel lengths of 45nm and 55nm, respectively. For the optimized cases, the yields are about 98% and 99%, respectively.

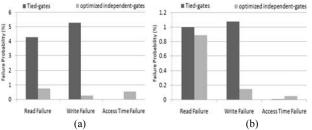

Fig. 4 shows how much failure probabilities change after the application of our technique. For the optimized cell, the main failure mechanisms (read and write failures) have decreased considerably while the access time failure has increased. Here, the read and write failures have decreased by increasing  $V_{\rm trip}$  and the strength of the access transistors, respectively. The write failure is the main failure component in the tied-gates cell as shown in Fig. 4. This is due to surface orientation effects, which result in more symmetric nFET and pFET, and hence, a harder write operation for the tied-gates cell [15]. The access time failure in the tied-gates cell is lower because during the read operation, the back-gate of both pull down and access transistors are connected to the front-gate which is connected to  $V_{\rm dd}$ . This results in the highest read current and lowest access time failure. However, in the

optimized cell, these voltages have lower values than  $V_{\rm dd}$ . Table II. Back gate voltages of the optimal cell.

| Tr.       | Back-Gate Voltage |                   |

|-----------|-------------------|-------------------|

|           | $L_{\rm g}$ =45nm | $L_{\rm g}$ =55nm |

| Pull up   | 0.05V             | 0.0V              |

| Pull down | 0.05V             | 0.15V             |

| Access    | 0.85V             | 0.9V              |

Fig. 3. Yield comparison of optimized and tied-gates SRAM cells for 45 and 55nm channel lengths.

Fig. 4. Failure probabilities components of the tied-gates and optimized independent-gates SRAM cells, a) 45nm, b) 55nm.

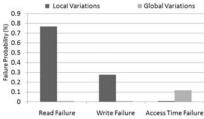

To study the effect of the local and global variations on the failure components, each of these variations were applied independently to our optimized cell for the 45nm channel length. The results are shown in Fig. 5. The read and write failures happen due to the mismatch in the cell transistors [17]. As the results show, the read and write failures are mainly due to the local variations which induce mismatch. On the other hand, the global variations give rise to more access time failures. The reason is that if the strength of the access or pull down transistor decreases, the strength of the other transistor also decreases enlarging the access time failure. Note that the sum of the two access time failures is less than that when they are applied simultaneously. This shows that access time failure depends more on the strength variation of the access or pull down transistor than on the relative strength variation of these transistors [17].

# VI. CONCLUSION

A method for optimizing the design of double-gate FinFET based SRAMs was presented. The method used a statistical optimization process to maximize the yield against process variations. SRAM read, write, and access time failure metrics were modeled and then the optimum back-gate voltages were found using particle swarm optimization. It was shown that by modulating the back-gate voltage of the three kinds of transistors in the SRAM cell, a much higher yield than the tied-gates version is achievable. The increase in the yield was 0.8% and 8.8% for the cells with the channel lengths of 55nm and 45nm, respectively. This shows the effectiveness of the proposed techniques increases as the devices shrinks.

Fig. 5. The probabilities of failure components of the optimized independentgates SRAM cells for the 45nm channel length due to local and global variations.

## REFERENCES

- International Technology Roadmap for Semiconductors 2009, http://www.itrs.net/Links/2009ITRS/Home2009.htm

- [2] K. Agarwal and S. Nassif, "The Impact of Random Device Variation on SRAM Cell Stability in Sub-90-nm CMOS Technologies," *IEEE Trans.* Very Large Scale Integration (VLSI) Syst., vol. 16, no. 1, pp. 86–97, Jan. 2008.

- [3] V. Gupta and M. Anis, "Statistical Design of the 6T SRAM Bit-Cell," IEEE Trans. Circuits Syst. I, vol. 57, no. 1, pp. 93–104, Jan. 2010.

- [4] S. Mukhopadhyay, H. Mahmoodi, and K. Roy, "Reduction of parametric failures in Sub-100-nm SRAM Array Using Body Bias," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 27, no. 1, pp. 174–183, Jan. 2008.

- [5] S. Tang et al., "FinFET-a quasi-planar double-gate MOSFET," in Proc. ISSCC Digest of Technical Papers, 2001, pp. 118-119.

- [6] Z. Guo et al., "FinFET Based SRAM Design," in Proc. ISLPED, 2005, pp. 2–7.

- [7] A. Datta et al., "Modeling and Circuit Synthesis for Independently Controlled Double Gate FinFET Devices," IEEE Trans. Comput.-Aided Design Integr. Circuits Syst., vol. 26, no. 11, pp. 1957–1966, Nov. 2007.

- [8] O. Thomas, M. Reyboz, and M. Belleville, "Sub-1V, Robust and Compact 6T SRAM cell in Double Gate MOS technology," in *Proc.* ISCAS, 2007, pp. 2778-2781.

- [9] K. Endo et al., "Independent-Double-Gate FinFET SRAM for Leakage Current Reduction," *IEEE Electron Device Lett.*, vol. 30, no. 7, pp. 757-759, Jul. 2009.

- [10] M. Rostami, B. Ebrahimi, and A. Afzali-Kusha, "Design Centering Scheme for Robust SRAM Cell Design," in *Proc. ICCCE*, 2008, pp. 871-877.

- [11] K. Kim and J. G. Fossum, "Double-gate CMOS: Symmetrical-versus asymmetrical-gate devices," *IEEE Trans. Electron Devices*, vol. 48, no. 2, pp. 294–299, Feb. 2001.

- [12] K. Kim, J. G. Fossum, and C. T. Chuang, "Physical compact model for threshold voltage in short-channel double-gate devices," in *Proc.* SISPAD, 2003, pp. 223–226.

- [13] T. Sakurai and A. R. Newton, "Delay Analysis of Series-Connected MOSFET Circuits," *IEEE J. Solid-State Circuits*, vol. 26, no. 2, pp. 122-131, Feb. 1991.

- [14] Sentaurus Device simulator from Synopsys Inc., Version X-2005.10.

- [15] M. Chowdhury et al., "Carrier Mobility/Transport in Undoped-UTB DG FinFETs," IEEE Trans. Electron Devices, vol. 54, no. 5, pp. 1125–1131, May 2007

- [16] Y. Taur et al., "A continuous, analytic drain- current model for DG MOSFETs," IEEE Electron Device Lett., vol. 25, no. 2, pp. 107–109, Feb. 2004

- [17] S. Mukhopadhyay, H. Mahmoodi, and K. Roy, "Modeling of failure probability and statistical design of SRAM array for yield enhancement in nanoscaled CMOS," *IEEE Trans. Comput.-Aided Design Integr. Circuits Syst.*, vol. 24, no. 12, pp. 1859–1880, Dec. 2005.

- [18] S. Rodriguez and B. Jacob, "Energy/power breakdown of pipelined nanometer caches (90 nm/65 nm/45 nm/32 nm)," in *Proc. ISLPED*, 2006, pp. 25–30.

- [19] D.D. Lu et al., "Compact Modeling of Variation in FinFET SRAM Cells," *IEEE Design & Test of Computers*, vol. 27, no. 2, pp. 44-50, Feb. 2010.

- [20] D.D. Lu et al., "Design of FinFET SRAM Cells using a Statistical Compact Model," in Proc. ISLPED, 2009, pp. 1–4.

- [21] Y. Shi, "Particle Swarm Optimization," Feature Article of IEEE Neural Network Society, February 2006.